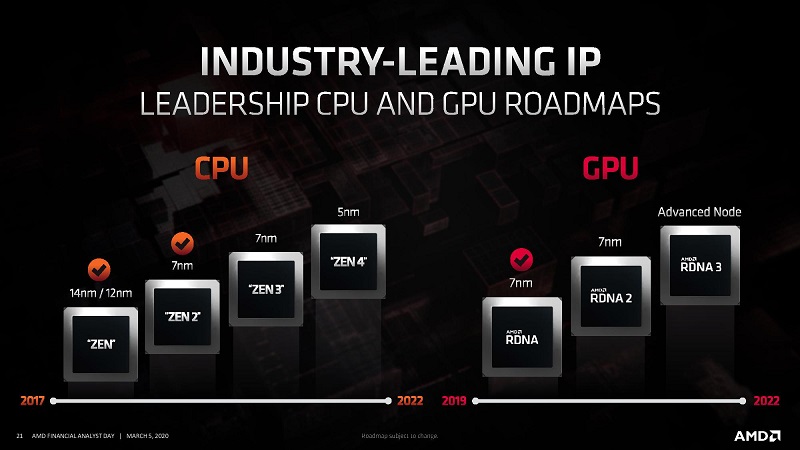

Говорихме за Zen 2 в обзор и хвалихме Zen 3 за напредналата кеш йерархия, а сега е време да поговорим за (близкото) бъдеще и AMD 3D V-cache. 3D стакинг техлогията на AMD и TSMC е почти недосегаема, но това не значи, че сянката на съмненията около крайните продукти е напълно изчезнала. Имаме глобален недостатък на суровини, безпрецедентно високото ниво на търсене и покачващи се цени. Възможно ли е да сме изправени пред технология, обречена на провал още в началото?

Съдържание

AMD 3D V-cache – crème de la crème за AM4?

Преди да започнем с анализ на 3D V-cache, нека направим кратък обзор на ситуацията, в която е възможно технологията да се реализра в продукти. Най-важният въпрос е свързан с това дали процесорите, използващи 3D V-cache ще бъдат електрически и физически съвместими с AM4. Също така, кога можем да видим първите продукти, базирани на технологията?

Вариант 1:

В този вариант получаваме съвместимост към края на 2021 г. или началото на 2022 г. с нова линия процесори. AM4 ще се превърне не само в един от най-дълголетните цокли за масовия пазар, но и с най-много поколения процесори за него. Това ще бъде силен прецедент в ума на консуматорите за AM5. Не е нечувано един цокъл да види промяна в DDR и да поддържа и старо, и ново поколение памет. Не е нечувано един и същи цокъл да поддържа и нов, и стар PCI-E интерфейс. Случи се съвсем скоро с PCI-E 4.0. Но при AM5 има потенциал да видим както нова памет, така и нов PCI-E интерфейс плюс и нови чипсети. Така, че нека разгледаме и втория вариант.

Вариант 2:

В него, AMD взима решение да разпредели новите поколения процесори и чипсети между два цокъла – AM4 и AM5. И това е разделението само за масовия пазар. Остава цялата им сървърна линия – EPYC – и необявени HEDT процесори – Threadripper. Това прави сегментацията не само сложна, но и потенциално проблемна. Дали новите технологии ще следват йерархия в графика си – първо сървър, после HEDT, после масови процесори? Малко вероятно, имайки предвид недостига на суровини, който споменахме. Intel бавно, но славно решават проблемите си с производството, защото са независими. AMD разчитат повече на TSMC и независимо какво правят, трябва да споделят капацитета на производителя си.

В крайна сметка, прототипа на работещ продукт беше от настоящото Ryzen 5000 поколение. Dr. Lisa Su потвърди, че ще видим първите продукти с 3D V-cache към края на 2021 г. Физическите размери на AM4 процесорите са ни добре известни, а от изтекли снимки на AM5 знаем, че те ще бъдат променени за новия цокъл. Спекулира се, че тази година ще видим реални процесори, използващи 3D V-cache и те ще бъдат съвместими с AM4.

3D стакинг технологията на AMD

3D чиплетите са началото на това ново пътешествие и първите стъпки засягат кеш-паметта. Макар да не е ясно точно какви ще бъдат бъдещите имплементации, това е изключително важна първа стъпка. Производствената технология се различава драстично от тази във Foveros, но това не е нужно да бъде нещо лошо. Преди почти две години говорихме за патентите на AMD за 3D стакинг и ето първите плодове от този труд.

Обем на 3D кеш паметта

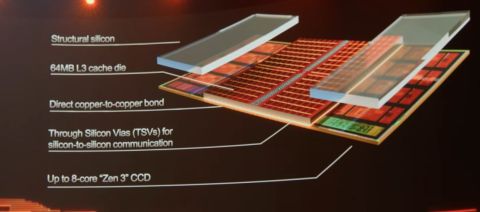

Показаната имплементация по време на Computex 2021 беше версия на Ryzen 9 5900X с 3D V-cache. За сравнение трябва да поставим на фокус оригиналния CCD в Ryzen 5000 серията – 8 ядра, които имат достъп до 32MB L3 кеш. В прототипа, този чиплет се превръща в 8-ядрен комплекс с достъп до 96MB L3 кеш. Според данни директно от AMD, общата пропускливост на тази кеш памет е над 2 TB/секунда. Това теоретично прави цялата L3 кеш памет по-бърза дори от L1 кеш паметта. Вероятно тази скорост е за сметка на латентност. Всичко това означава, че в процесори, използващи 8-ядрени CCD, общият обем на L3 кеш памет ще бъде: N (брой CCD) х 96MB = общо количество L3 кеш. При процесори като Ryzen 9 5900X или Ryzen 9 5950X, това ще означава 192MB L3 кеш. При процесори с по-голям брой комплекси, цифрата ще става само още по-потресаваща.

Физически размери

Общият размер на един Zen 3 CCD е 80.7 mm², а размерът на 3D V-cache чипа е 36 mm2. Това налага и добавянето на допълнителен структуриращ субстрат. Това спомага за равномерно разпределяне на натиска между долния (изчислителен) чип и горния (кеш) чип. Пакета и на двата чипа е допълнително изтънен с идеята новите CCD да запазят физическия си размер същия. Това може би ще помогне на технологията да понижи цената си донякъде, тъй като запазва технологията за крайно пакетиране, използвана и в Ryzen 5000 серията.

Дизайн

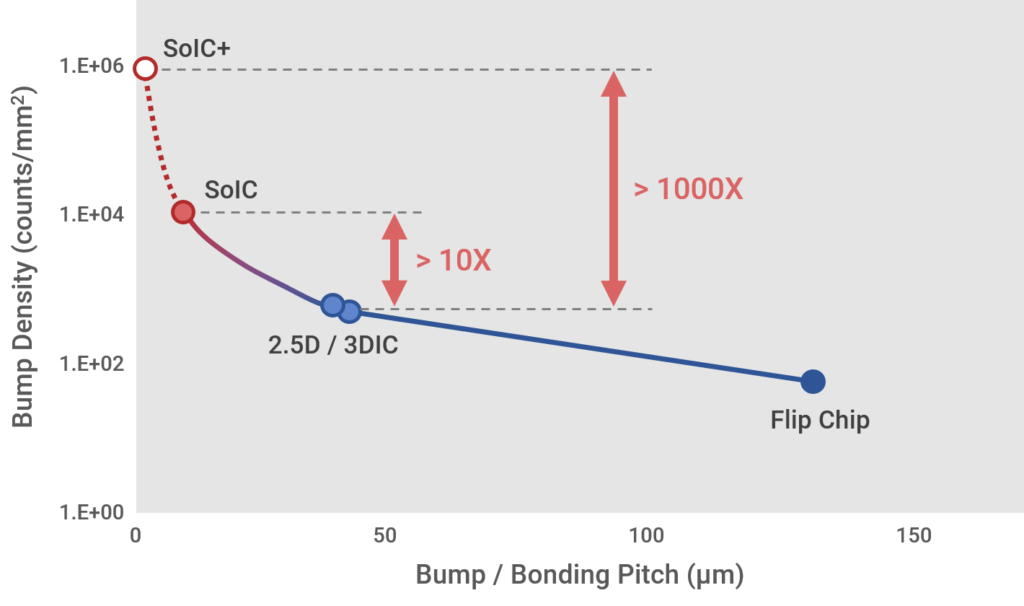

Освен изтъняването, двата субстрата (чип и кеш) са свързани с многобройни TSV (Through Silicon Via) съединения. В дизайн без микро-неравности (microbump-less design), TSV имат огромен потенциал за енергоспестяване и увеличена пропускливост. Можем да видим пример за това от данните за Lakefield, където публично достъпната информация дава 0.15 pJ/bit консумирана мощност за трансфер на данни във Foveros пакета. При V-cache, информацията към момента гласи, че можем да очакваме по-скоро около 0.05 pJ/bit – или около 1/3 в сравнение с „традиционния“ дизайн!

За разлика от microbump дизайна на Foveros, тук няма възможност за полагане на изчислителен хардуер на всички нива. Ето защо и първата имплементация на технологията е с ядро + кеш и съдържа само две нива. Това не означава, обаче, че производственият процес зад технологията е ограничен до тези параметри. Нека поговорим за него.

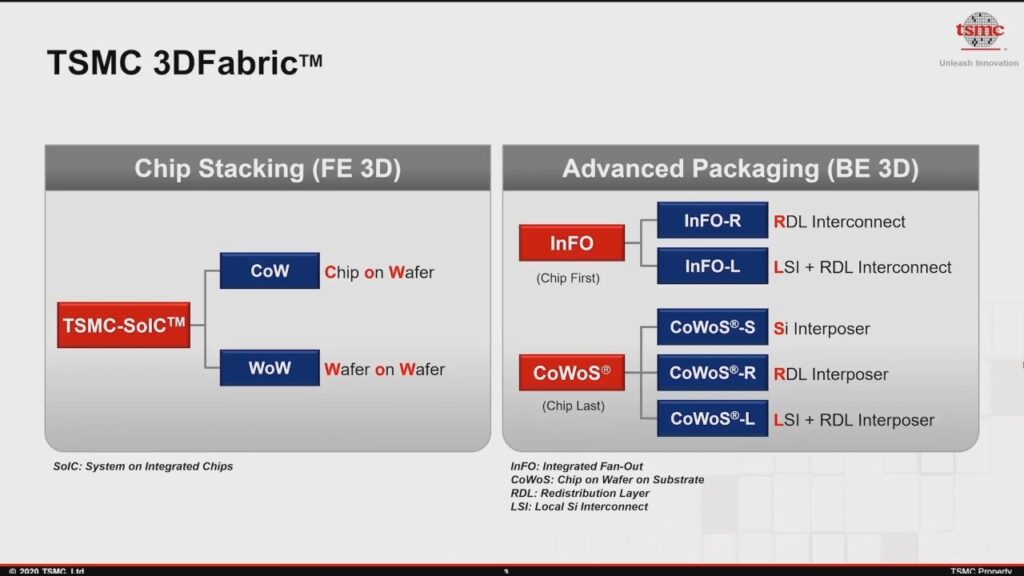

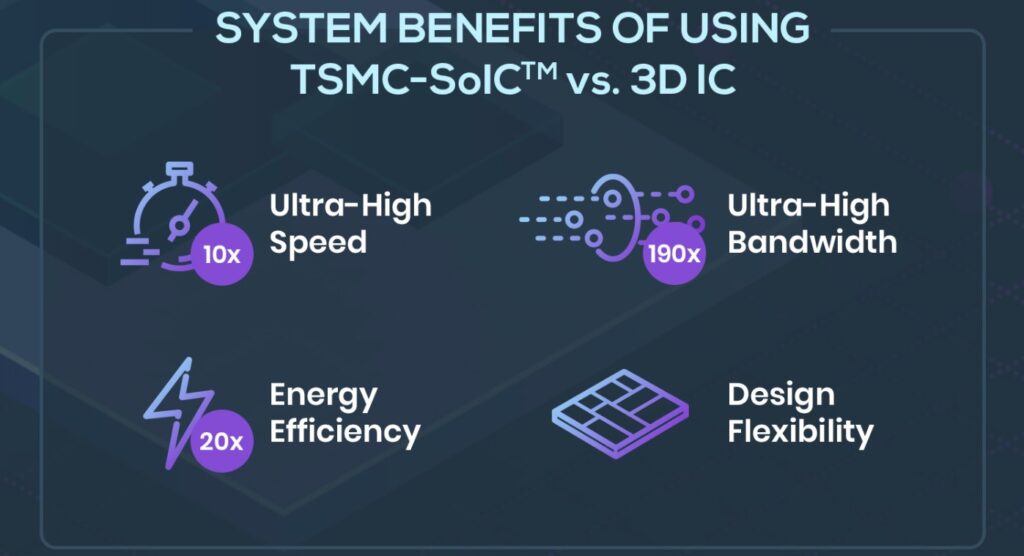

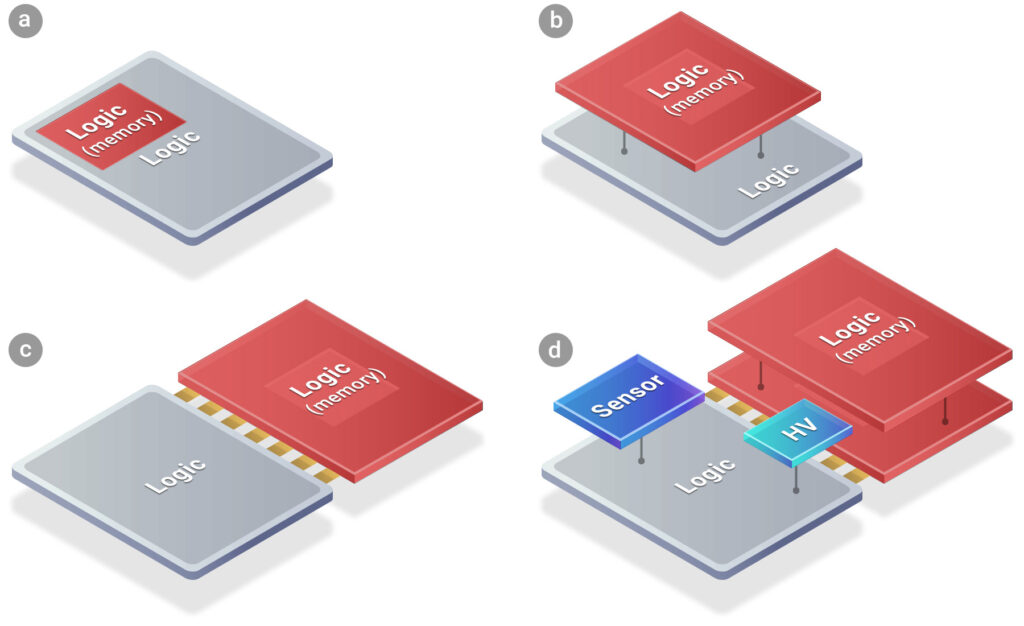

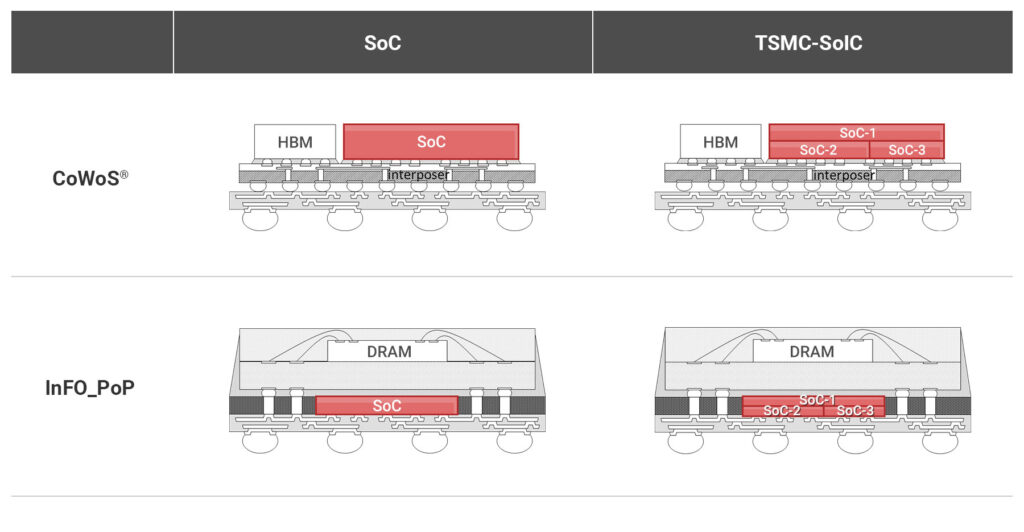

TSMC 3DFabric – запазената марка зад AMD 3D V-cache

AMD се възползва от SoIC CoW технологията на TSMC. Тъй като това е статия за 3D V-cache, не за технологията на TSMC, ще се съсредоточим предимно върху имплементацията на 3DFabric по отношение на 3D V-cache. Все пак, ето някои от основните положения в 3DFabric. 3D връзките са значително по-къси от 2D вариантите. Ето защо 3D IC като цяло е революционен напредък в производствения процес. SoIC технологията на TSMC прави още една стъпка напред, запазвайки формулата за вертикално свързване между слоеве (до 12 според производителя!), но премахвайки нуждата от микро-неравности.

Както вече казахме многократно, това прави връзките още по-къси, преноса на данни още по-ефикасен и бърз и дава възможност за много по-голяма гъвкавост в дизайна. Патентите на AMD за охлаждане на 3D стакове разчитат точно на силните страни на тази технология. Неслучайно и данните за преимуществата на AMD 3D V-cache съвпадат с цифрите от изображението долу.

Недостатъците на технологията се свеждат до невъзможността за вертикално трупане на изчислителни елементи един върху друг. При Foveros това е възможно. Проблемите за преплитане и смущения са налице и в двата случая, но термалните ограничения са много по-големи при струпване на активни/изчислителни елементи. Ето защо и имплементацията в кеш-памет, която е термично пренебрежима, е перфектната платформа за по-нататъшно рафиниране. По-малко усложения = по-достъпна технология = по-обширно ползване.

Важни детайли около интеграцията

Цялостната интеграция на този чип с кеш-памет поражда редица въпроси:

- Как е решен проблема с температурите?

- Къде точно е поставен чипa, спрямо логиката (ядрата) в комплекса?

- Какви функции изпълнява допълнителния структурен субстрат?

- Как се събира повече памет на по-малко място в същия производствен процес?

- Каква ще бъде кеш йерархията и остава ли все пак интегрирания L3 в самия CCX?

Отговорите на 1 и 3 се припокриват – допълнителният субстрат има и термодинамични свойства, разпределяйки и/или провеждайки топлината от ядрата. Това е важно и за отговора на 2 – новият кеш не съвпада с горещите точки на ядрата. Що се отнася до обема, TSMC разполага с множество библиотеки за своите производствени процеси. Това важи с пълна сила и за 7nm. AMD ще се възползва от специализирани библиотеки, оптимизирани за производство на SRAM, каквато е и кеш паметта. Това дава възможност за мащабно производство, което освен това е и максимално оптимизирано за крайния му продукт.

Кеш йерархията е може би един от най-интересните моменти. Крайното решение (поне за първото поколение продукти) е изключително балансирано. Кеш модулът е поставен на основната L3 кеш памет в основния CCX и ще бъде със сдвоени адреси. По този начин 3D V-cache ще бъде неразличима от интегрираната L3 кеш памет. Интересно е, че вертикално интегрирания кеш модул ще бъде в същата верига като L3 кеша, интегриран в комплекса, но въпреки това ще има контрол над консумацията на 3D V-cache чипа.

Крайни резултати

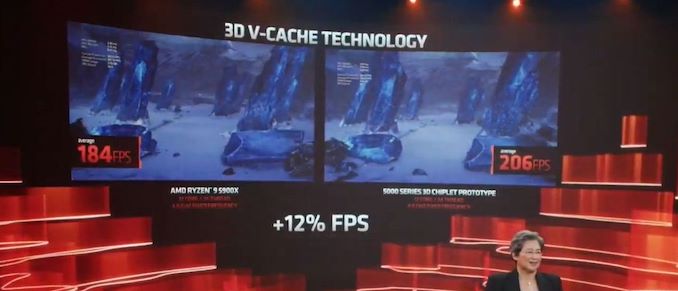

Това е снимка от презентацията по време на Computex 2021. Имаше дадени и още няколко примера:

- DOTA2 (Vulkan): +18%

- Gears 5 (DX12): +12%

- Monster Hunter World (DX11): +25%

- League of Legends (DX11): +4%

- Fortnite (DX12): +17%

Не забравяйте, че резултатите са с прототип и то на Ryzen 5000 процесор. Цифрите са изключително подобни на такива, илюстриращи скок от промяна в архитектурата, но това не е случая. Това е стандартен чип, който има промяна само в пакетирането и обема на кеш паметта си. Със сигурност можем да очакваме още по-големи цифри при интеграции в нови архитектури или специализирани натоварвания, но дори показаното е впечатляващо.

Това е същият процесор, произведен със същата литография и най-важното – съвместим със същия цокъл. Но, дали крайният продукт ще отговаря на всички тези параметри? Предстои ни да разберем още към края на тази година. Ако и вие очаквате с нетърпение, със сигурност ще намерите своето място във фейсбук групата ни – Технологичното общество на България – така, че заповядайте!

Technology.bg Светът на технологиите

Technology.bg Светът на технологиите

Възможности за интеграция и свързване

Възможности за интеграция и свързване

Пълна гъвкавост в интеграцията на многомодулни чипове

Пълна гъвкавост в интеграцията на многомодулни чипове

Лицето на революцията

Лицето на революцията