AMD Zen 3 процесорите се очакват официално на 08.10. 2020 г. Октомври ще бъде зает месец за компанията, защото на 28.10.2020 г. очакваме още един анонс. Той ще бъде за идното поколение графични карти с RDNA 2 архитектура. Докато получим допълнителна официална информация има още седмици. На кого му се чакат седмици? Не и на нас! Четете следващите редове за първата изтекла техническа информация относно предстоящите AMD Zen 3 процесори.

Съдържание

AMD Zen 3 – в очакване на съвършената кеш йерархия

Изтеклият документ ни предоставя информация относно някои ключови разлики спрямо предишните Zen архитектури. За по-лесна четимост ще правим сравнения основно с Zen 2 процесорите на AMD, за които вече сме правили архитектурен обзор. Без повече забавяния, ето и ключовите специфики от изтеклия документ.

L2 кеш

Всяко Zen 3 ядро ще разполага сe 512 KB L2 кеш памет. Интересното при Zen 3 ще бъде, че всеки CCD в това поколение ще разполага само с един CCX с до 8 ядра. Това означава, че при AMD Zen 3 архитектурата ще имаме до 8 ядра в един чиплет (CCD) за общо до 4 MB L2 кеш. Ядрата във всеки един CCD могат да работят, както в 1Т режим, така и в 2Т режим (Т = threat = нишка). По този начин, един 16-ядрен Zen 3 процесор ще може да бъде изграден само с два чиплета по 8 ядра и ще разполага с общо 8 MB L2 кеш.

L3 кеш

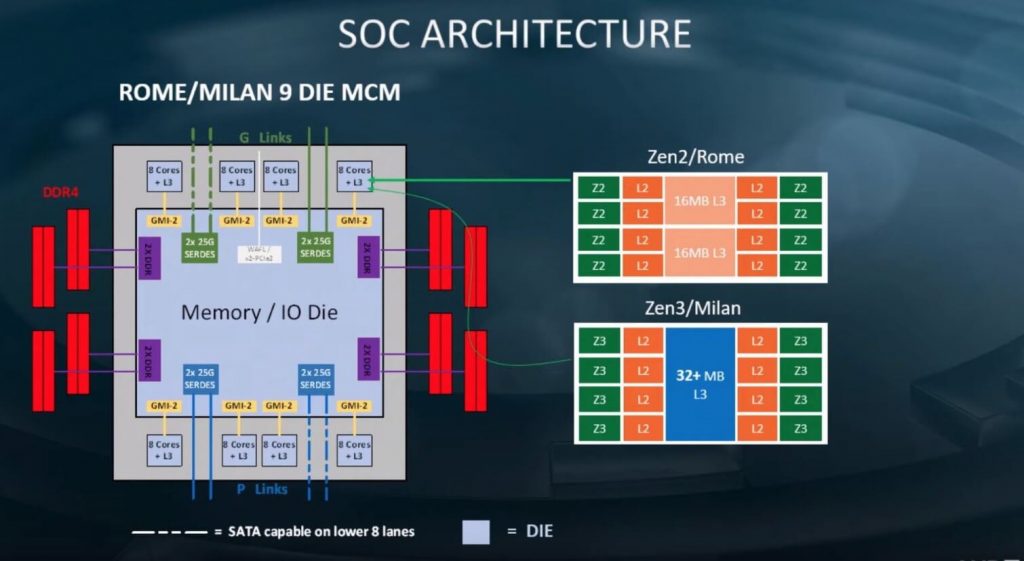

Още една интересна промяна в кеш йерархията е свързана с L3 кеш паметта. В Zen 3 ще имаме уницифицирана L3 кеш – до 32 MB за всеки CCD. Това е огромна промяна в сравнение с предишни дизайни, за която говорихме още в обзора на Zen 2 архитектурата. Наистина си струва да се върнете и да го прегледате. При Zen 2 наблюдавахме всеки един CCD с до 2 CCX-а с до 4 ядра. Тук имаме повече ядра на едно място, което намалява латентността (също го обсъдихме в обзора на Zen 2 – наистина, не знам защо още четете тук, върнете се първо там).

Обобщение

Това ще бъде предпоставка за огромни скокове в производителността за някои сценарии. За останалите, можем спокойно да кажем, че е важна предпоставка за подобрена производителност при товари върху малък брой ядра/нишки. Това беше проблем за Zen 2, където всеки CCX разполага с до 16 MB L3 кеш. Макар в един Zen 2 CCD с два CCX с по 16 MB кеш да получаваме същият обем от памет (32 MB), в Zen 3 тази памет е достъпна за всички ядра с еднаква латентност. При разделението на ядрата в два отделни CCX се създава допълнителна латентност при комуникацията между отделните ядра в отделните CCX и кеш памети.

TLDR: 1 Zen 3 CCD съдържа един CCX, а при Zen 2 бяха два. Един CCX съдържа до 8 ядра с до 16 нишки, а при Zen 2 бяха до 2 х 4 ядра. Повече ядра в един CCX намаляват нуждата от комуникация между чиплетите и така новата архитектура дава възможност за унифициране на L3 кеш паметта, което води до допълнителни ползи в определени сценарии. Тази информация беше изтекла преди време по отношение на Milan – кодовото име за EPYC линията на AMD със същата архитектура.

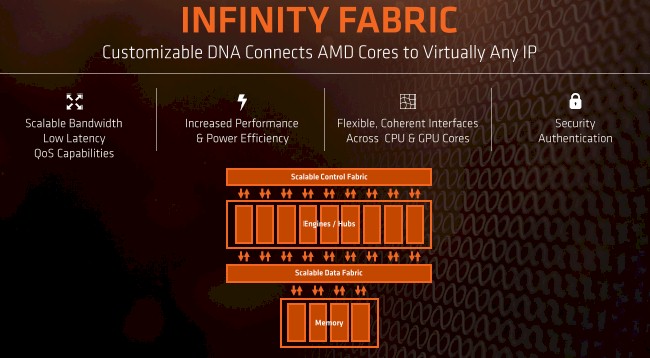

Infinity Fabric – допълнения и подобрения

AMD Ryzen 4000 серията с кодово име Vermeer за настолни процесори ще представи и подобрения в свързващата Infinity Fabric (IF) архитектура и преноса на данни. Очакваме подобрена поддръжка на DRAM – до 512 GB на канал или цели 1 TB за ECC памет. Въпреки увеличения обем, официално поддържаната скорост остава DDR4-3200. Към процесора ще има два унифицирани контролера за памет. Всеки от тях ще поддържа по един канал, което дава възможност за 2 DIMM модула на всеки канал. Подобренията в свързващата архитектура са комплексни, но не засягат всяко едно ниво от структарата ѝ. Отново с цел опростяване, следват характеристики на I/O чиплета (IOD), преведени и синтезирани от нас (директно от изтеклия документ):

- Отговаря за двупосочния трафик на данни

- Съгласува сигналния трафик (отговаря за кохерентността на данни – в случая, тези до 512 GB/канал)

- Интегрира I/O APIC и отговаря за IRR (interrupt request routing)

- GMI2: това са специални портове за данни между IOD и всеки чиплет; в Zen 3 виждаме до 2 такива на всеки CCD, което де факто удвоява комуникацията между I/O на чипа и ядрата във всеки CCD.

Още благинки и коментари

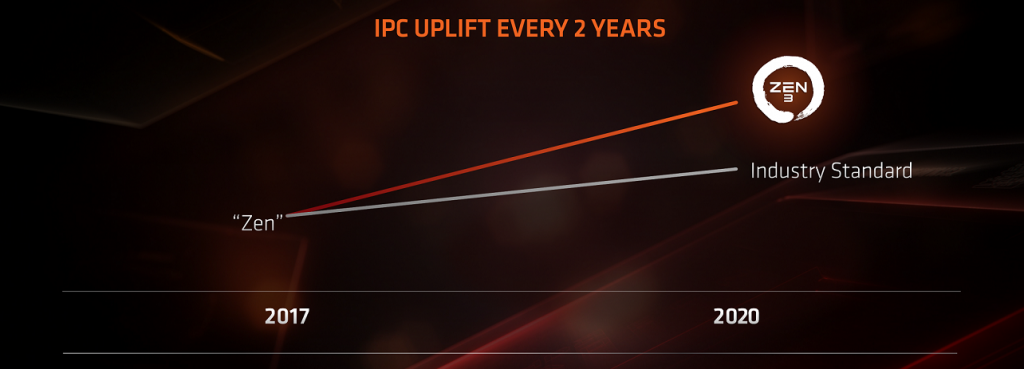

⇒ Очакваме сериозен скок в IPC (слуховете са за ~17%), което ще помогне на компанията в борбата за първото място при натоварвания с по-малка паралелност или по-малко натоварени ядра и нишки.

⇒ Нови подобрения в сигурността на чиповете на архитектурно ниво – досегашната технология AMD Secure Processor вече ще носи и ново име – Platform Security Processor (PSP). PSP ще дойде и с нов контролер (а защо не и с нов ARM чип?).

⇒ Фокуса на компанията за това поколение е в три посоки: по-високо IPC, по-високи честоти и по-добра енергийна ефективност.

⇒ Новите процесори ще продължат да бъдат съвместими с AM4 сокета – както беше обещано преди повече от три години.

⇒ Цитат от Rick Bergman – Изпълнителен Вицепрезидент в Computing & Graphics дивизията на компанията:

И какво следва за AMD в PC сферата? Ами, не мога да споделя твърде много, но мога да кажа, че нашето пътуване към по-висока производителност продължава с първите ни Zen 3 процесори, които по график ще бъдат пуснати на пазара по-късно тази година. Ще завърша, казвайки че все още не сте видели най-доброто, на което сме способни…

⇒ Все още нямаме яснота за цените при AMD Zen 3 процесорите – знаем само, че ще са по-бързи, по-мощни и още по-ефикасни.

Ако имате още информация по темата или просто искате да си говорим за процесори и всякакви технологии, заповядайте в групатата ни – Технологичното общество на България. Обичаме да си говорим за компютри, телефони, софтуер, технологични новини и събития и още. Очакваме ви!

Technology.bg Светът на технологиите

Technology.bg Светът на технологиите