„Законът на Мур е мъртъв!“ – фразата, която се повтаря най-често в света технологиите през последните 5 години. Макар „законът“ да не е точно закон, а по-скоро наблюение, последиците от „смъртта“ му са всеобхватни. Монолитните еднопластови силициеви чипове са минало. Чиповете на бъдещето са многопластови и съдържат в себе си повече от транзистори. Новите патенти на AMD за 3D stacking са показателни, че компанията има възможност да подготви подходящо портфолио, но дали ще видим истински продукти скоро? Заинтересовани ли сте да научите повече? Хайде, ще отнеме не повече от 9 минути.

Съдържание

Законът на Мур

Тази статия се отнася за новите патенти на AMD, но преди това е важно да придадем контекст на значението им. Най-общо казано, Гордън Мур (съоснователят на Intel) е направил предсказание, свързано с увеличаване на производителността на процесорите чрез увеличаване плътността на транзистори върху чиповете. Важно е да се отбележи, че още Мур през 1998г. е предвидил експоненциалното покачване на производствената стойност на чиповете в следствие на увеличената им сложност. В този ред на мисли, е очевидно, че дори предстаказаното увеличение в изчислителната мощ да е правилно, ако се стига до него чрез увеличаване гъстотата на транзисторите, всеки следващ скок в производителността ще става все по-скъп. И ето къде започва историята за новите патенти на AMD.

Новите патенти на AMD

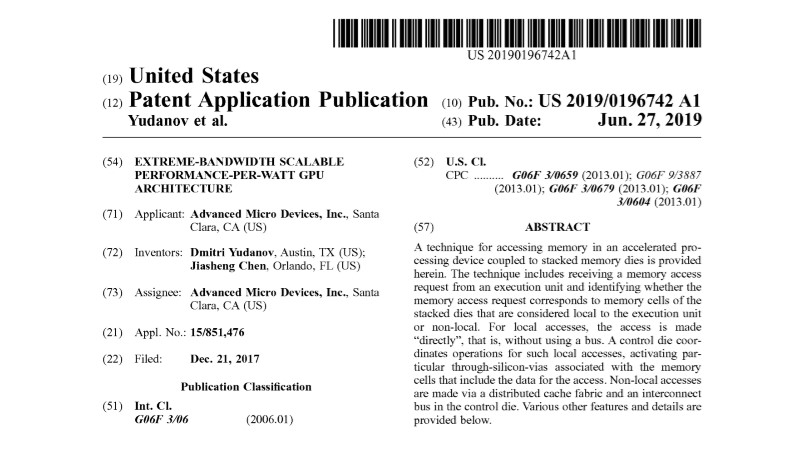

Можете да видите цялата технология в самия патент напълно безплатно. Пак заповядайте, нърдове! Идеята на AMD е проста – увеличаване на пропускливостта на данни за всеки индивидуален чип, поставяйки модули памет директно върху изчислителните му части. Макар и проста цел, постигането й изисква сериозни инжинерни иновации, защото това поражда редица проблеми като например:

- нуждата от високоскоростен интерфейс между изчислителната част и паметта

- завишена производствена комплексност и по-ниски успешни добиви

- охлаждане (патент за него тук)

Технически детайли

Тъй като патентите не са най-интересното четиво (за повечето хора), ще се опитаме да ви предоставим основната информация в кратки и лесно смилаеми параграфи. Ще започнем с прости неща като техническо изпълнение и затруднения и ще продължим с кратки анализи.

Какво и как?

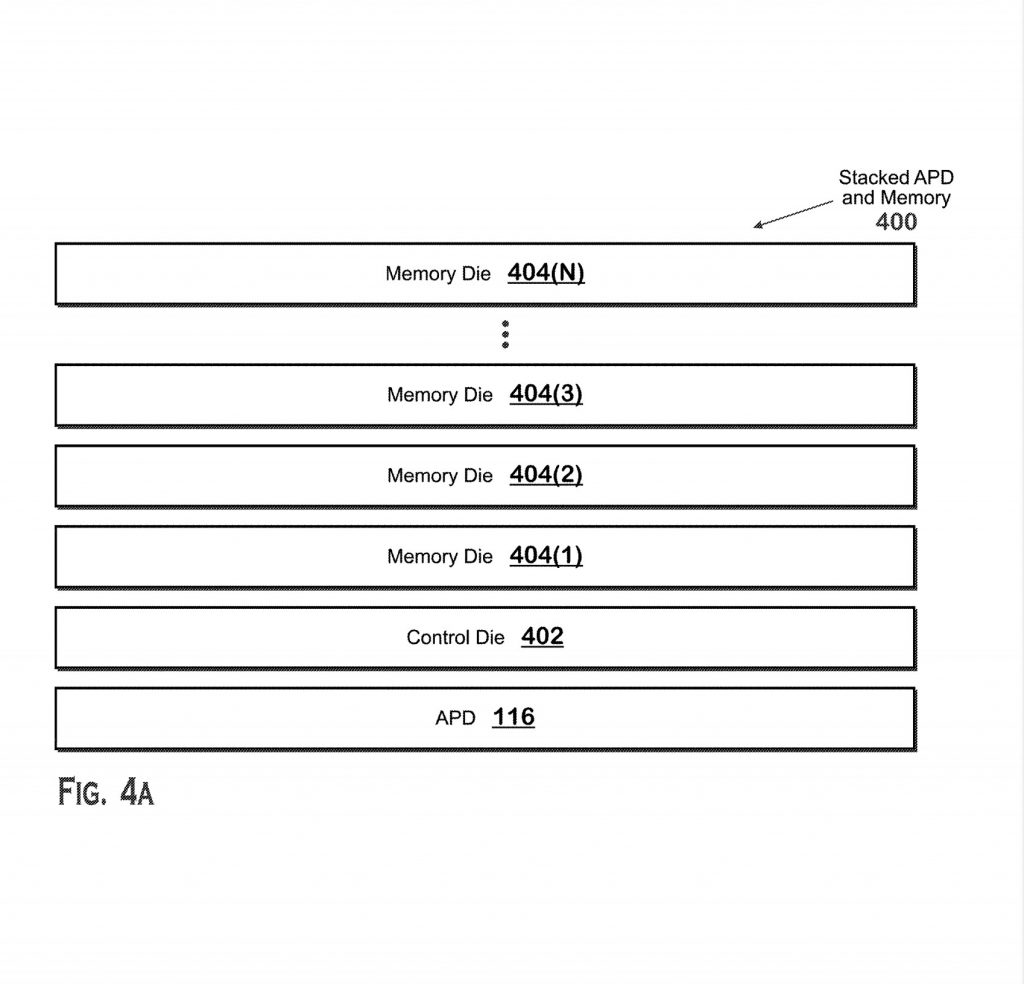

В най-простата си форма, новите патенти на AMD за 3D stacking ни показват разпределението на хардуерни елементи между отделните слоеве на цялостния чип. Показаната информация по-долу се отнася до патент, засягащ нова архитектура за графични ядра.

- Най-долен слой, съдържащ изчислителните елементи на ядрото. (APD 116)

- Среден слой, наречен Control Die, съдържащ неизчислителни елементи, като контролера за паметта и свързващия интерфейс например. (402)

- Най-горните слоеве съдържат чиповете на самата памет. (404)

Кратък анализ

Вторият слой съдържа ключа към успеха. Всичко се свежда до скоростта на свързващия интерфейс. Тя трябва да бъде достатъчно висока, за да бъдат оправдани всички затруднения, свързани с тази производствена философия. Към момента AMD използват патентованият си Infinity Fabric (IF) за комуникация между отделните елементи, разположени на силициевия субстрат. Предстои да разберем дали IF може да бъде приложен в новия производствен дизайн или компанията има нови решения.

Комуникация между отделните слоеве

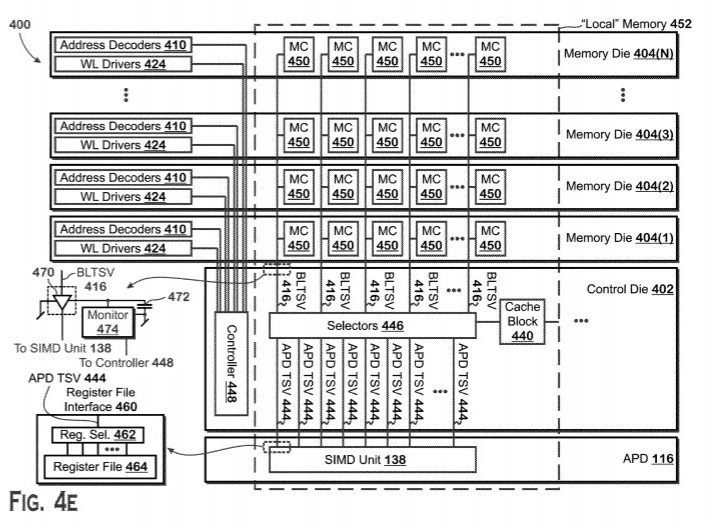

Infinity Fabric е интерфейс за комуникация между отделни чипове, но не може да бъде използван за преминаване до други нива в силициевата матрица. За тази цел се използват многобройни TSV – through silicon via. Освен че дават възможност за „междуетажна“ комуникация, TSV позволяват свързването на няколко компонента от различни чипове памет, използвайки един единствен TSV. Това е от огромно значение, защото позволява функционалното обединяване на отделните слоеве памет.

Кратък анализ

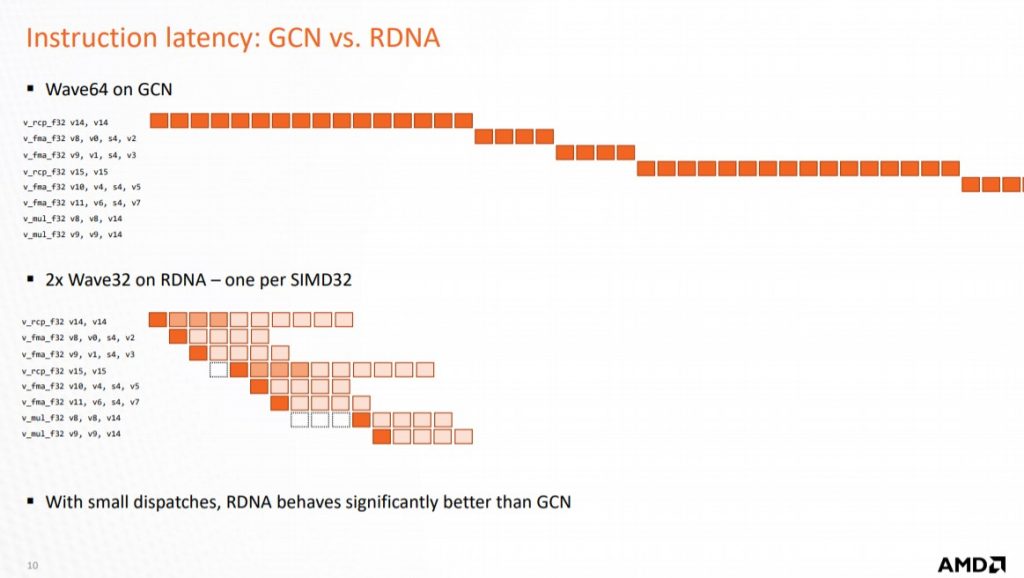

Преди да започнем, е важно да обясним какво значи SIMD – single instruction, multiple data. Това е от значение за определението, което AMD дават за „директна комуникация“ и е ключов момент в разбирането на енергийната ефикасност на тази архитектура. Директната комуникация е липса на свързващ интерфейс. „Локалната памет“ – номер 452 в диаграмата по-горе, е всъщност сбор от „запазени“ паметни чипове. Това са чиповете, запазени за директен достъп (без нужда от свързващ интерфейс).

Тази фрагментация позволява промяна в работата на всеки един SIMD. Преходът от wave64 към wave32 инструкции подобрява способността за паралелизиране на работния процес в специфични ситуации – както видяхме в Navi (RX 5700 и RX 5700XT). В този 3D модел обаче виждаме какъв всъщност е истинският потенциал за енергийна ефикасност, идващ от тази промяна. Ако инструкцията не съдържа в себе си маркер за запълване на едно от оранжевите блокчета горе, TSV връзката между SIMD и запазената му клетка памет няма да бъде активна.

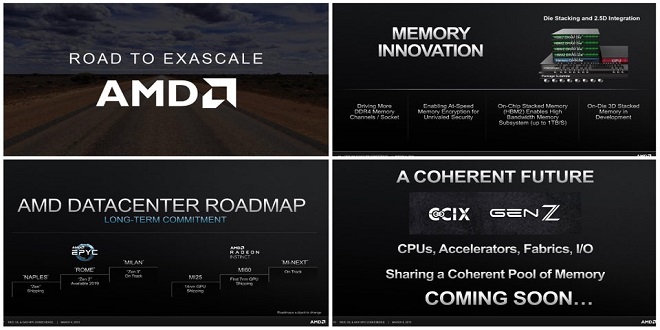

Селективната активност означава и по-нисък енергиен бюджет за целия Control Die. Това, което повдига сериозни въпроси, е всъщност обратният сценарий – дали всички изчислителни елементи могат да използват „запазената“ си клетка памет едновременно? За целта трябва всеки SIMD да има собствена TSV връзка към определена част от паметта. Последствията от подобна възможност са от огромно значение. Подобна архитектура би позволила невиждана досега пропускливост на данни – по-голяма дори от тази на HBM2! Големите изчислителни центрове и сървърни ферми търсят подобно решение още от създаването си…

Ами Foveros?

Intel изглежда са били първи на пазара с тази идея и съдейки по патентите на AMD, технологията ще бъде по-различна. Най-малкото, патентите на AMD са свързани с графични карти и системи за охлаждане на новите 3D stacked чипове. Освен това все още не е ясно дали ще видим краен продукт от AMD, използващ технолгията, докато Intel имат „готови“ процесори, базирани на нея.

Защо всичко това е важно?

AMD имат уговорка с GlobalFoundries за изпълнение на поръчкови таргети с 12-нанометрови чипове до 2021 г., въпреки че самата уговорка е със срок до 2024 г. Също така 7-нанометровите матрици са със значително по-висока цена от всички останали на пазара. В този смисъл производителността на кв.мм придобива още по-силно финансово значение. 3D stacking технологията позволява създаването на мощни чипове с по-малки размери, което намалява производствените разходи за суров материал. Това от своя страна решава част от проблема с покачването на цените на силициевите матрици. Всички печелят?

Освен това, състезанието към спазване Закона на Мур не е приключило – компаниите все още се опитват да увеличават гъстотата на транзисторите върху чипа. 3D stacking, нови производствени материали (освен силиций), 7 нанометра, 5 нанометра, 3 нанометра и т.н. – всичко това има еднакво значение за нас, потребителите. Следващите 5 години ще бъдат по-вълнуващи от последните 10!

Technology.bg Светът на технологиите

Technology.bg Светът на технологиите